TOSHIBA Bipolar Linear Integrated Circuit Silicon Monolithic

# **TA1318N**

## SYNC Processor, Frequency Counter IC for TV Component Signals

TA1318N is a sync processor for TV component signals.

TA1318N provides sync and frequency counter processing for external input signals.

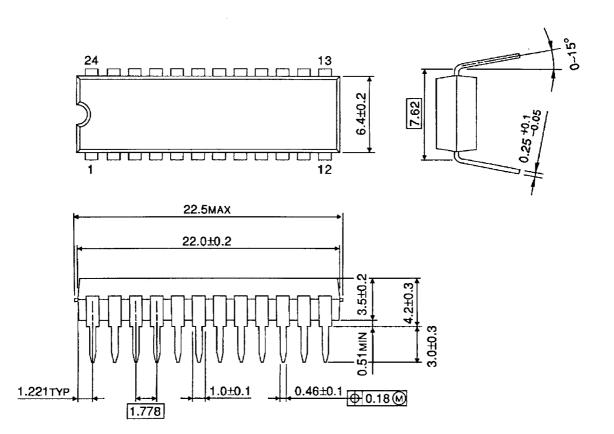

These functions are integrated in a 24 pin dual-in-line shrink-type plastic package.

TA1318N provides  $I^2C$  bus interface, so various functions and controls are adjustable via the bus.

# SDIP24-P-300-1.78

Weight: 1.22 g (typ.)

#### **Features**

- Horizontal synchronization circuit (15.75 kHz, 31.5 kHz, 33.75 kHz, 45 kHz)

- Vertical synchronization circuit (525I, 525P, 625I, 750P, 1125I, 1125P, PAL 100 Hz, NTSC 120 Hz)

- Horizontal and vertical frequency counter

- Horizontal PLL

- Accepts 2-level and 3-level sync

- · Accepts both negative and positive HD and VD

- Clamp pulse output

- HD, VD output (polarity inverter)

- Separated sync output

- Mask for the copy guard signal

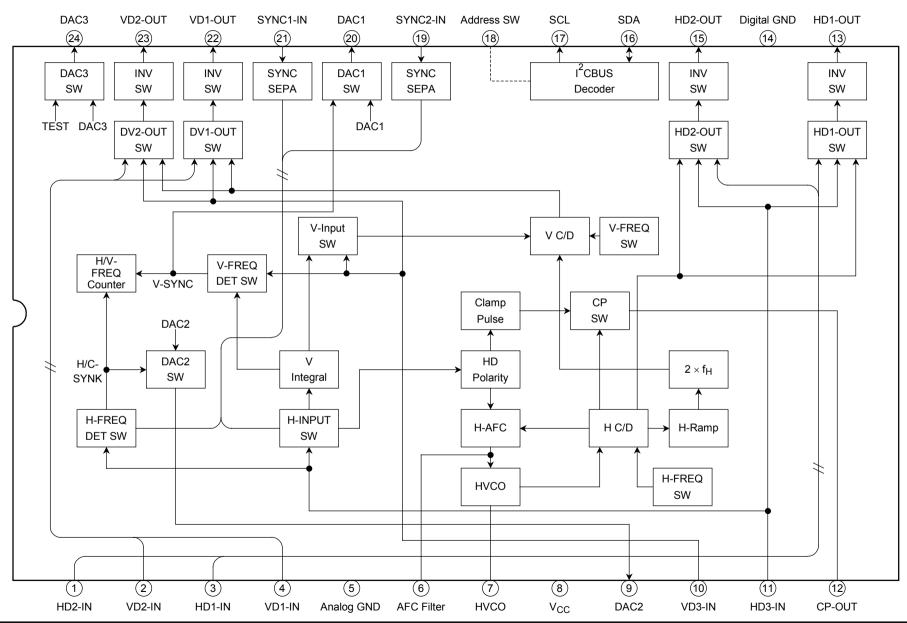

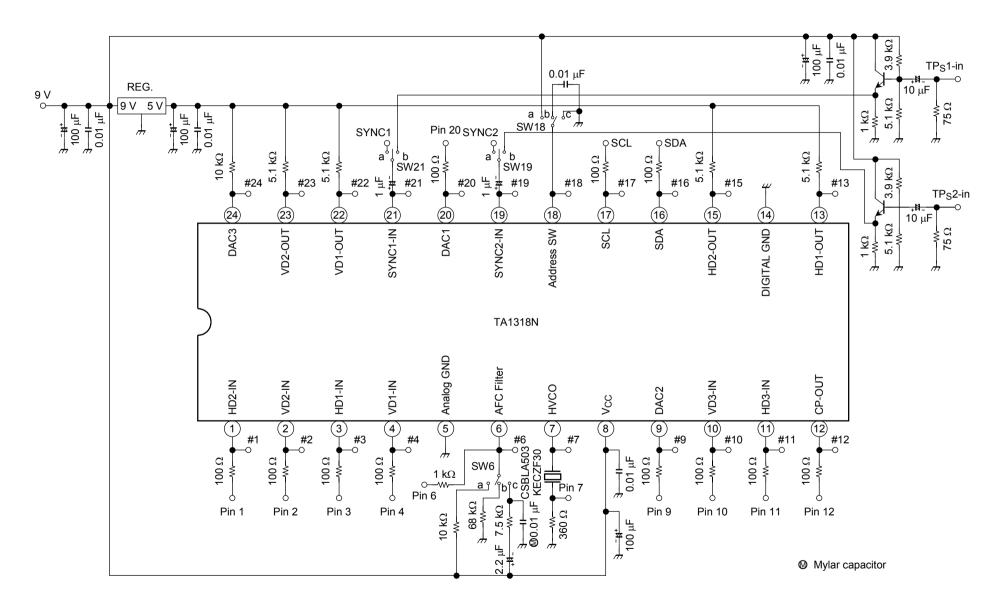

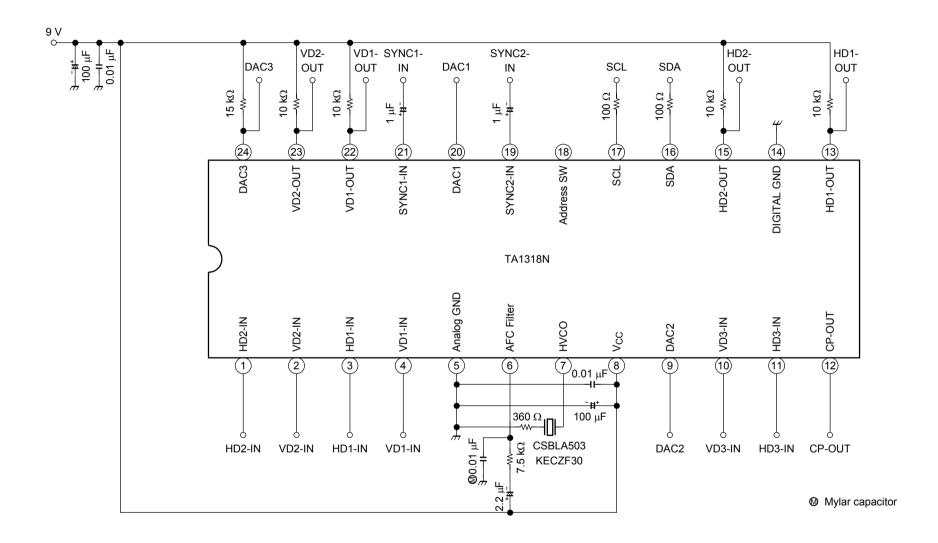

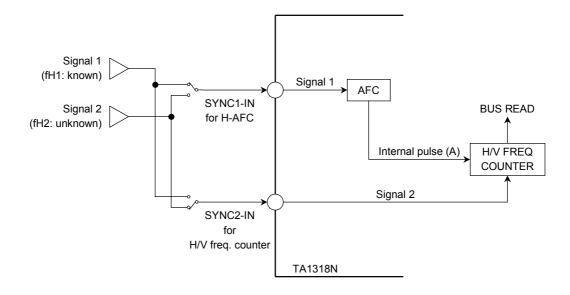

## **Block Diagram**

# **Pin Functions**

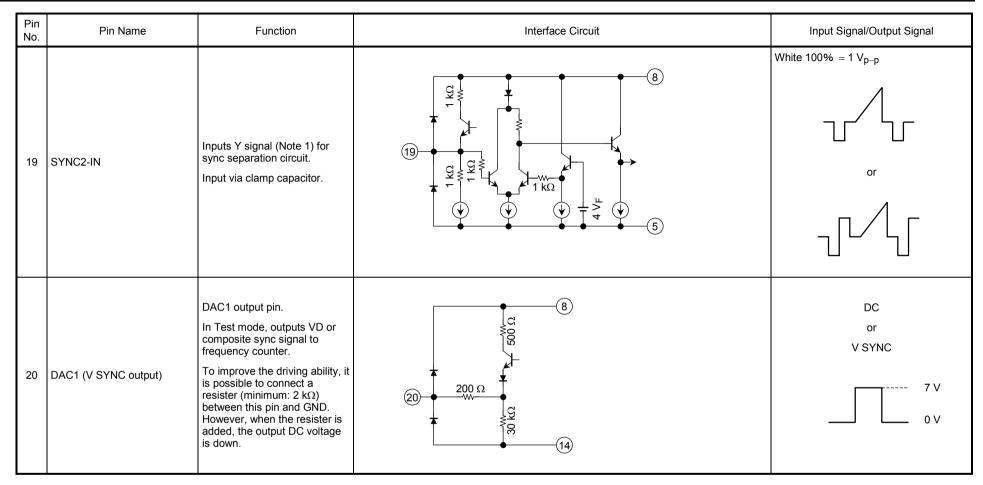

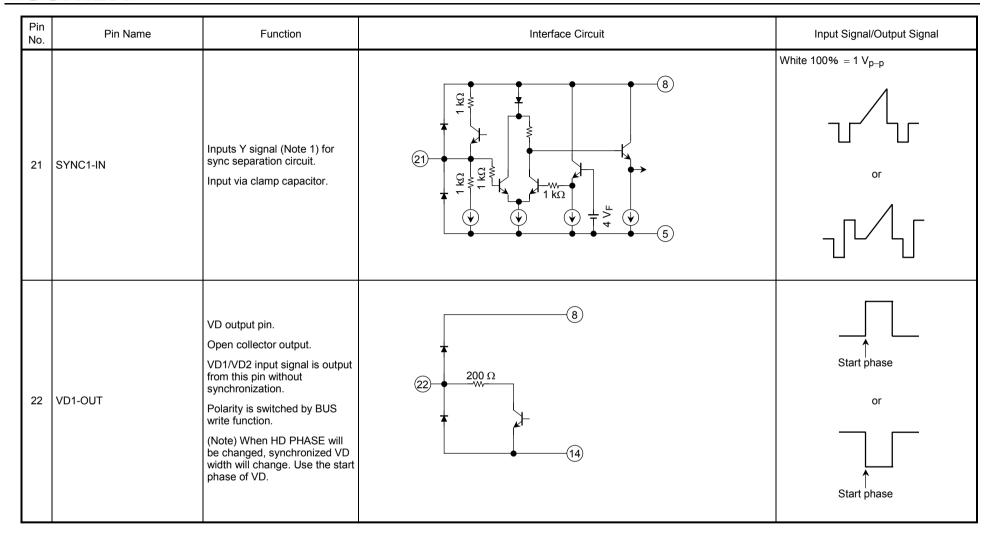

| Pin<br>No. | Pin Name | Function                                                                                                                               | Interface Circuit                                                                  | Input Signal/Output Signal |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------|

| 1          | HD2-IN   | Inputs horizontal sync signal.  Accepts input of both positive and negative polarity.  Input signal from this pin is not synchronized. | 1 kΩ<br>ΩY<br>ΩY<br>ΩY<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ<br>ΣΥ | or Th: 0.7 V               |

| 2          | VD2-IN   | Inputs vertical sync signal.  Accepts input of both positive and negative polarity.  Input signal from this pin is not synchronized.   | 2 1 kΩ CX W 5                                                                      | or Th: 0.7 V               |

| Pin<br>No. | Pin Name   | Function                                                                                                                               | Interface Circuit | Input Signal/Output Signal |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|

| 3          | HD1-IN     | Inputs horizontal sync signal.  Accepts input of both positive and negative polarity.  Input signal from this pin is not synchronized. | 3 1 KG CY OG 5    | or Th: 0.7 V               |

| 4          | VD1-IN     | Inputs vertical sync signal.  Accepts input of both positive and negative polarity.  Input signal from this pin is not synchronized.   | 4 1 kΩ            | or Th: 0.7 V               |

| 5          | Analog GND | GND pin for analog circuit blocks.                                                                                                     | _                 | _                          |

# **TOSHIBA**

| Pin<br>No. | Pin Name        | Function                                                                                         | Interface Circuit                    | Input Signal/Output Signal |

|------------|-----------------|--------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------|

| 6          | AFC Filter      | Connects filter for horizontal AFC.  Voltage on this pin determines horizontal output frequency. | 8<br>300 Ω 30 kΩ<br>5                | DC                         |

| 7          | HVCO            | Connects ceramic oscillator for horizontal oscillation. Use Murata CSBLA503KECZF30.              | 4 kΩ<br>Ω<br>Ω<br>1 kΩ<br>10 kΩ<br>5 | _                          |

| 8          | V <sub>CC</sub> | VCC pin.<br>Connects 9 V (typ.).                                                                 | _                                    | _                          |

# **TOSHIBA**

| Pin<br>No. | Pin Name                | Function                                                                                                                                                                                                                                                                              | Interface Circuit                                       | Input Signal/Output Signal                                   |

|------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|

| 9          | DAC2 (H/C. SYNC output) | DAC2 output pin. In Test mode, outputs HD or composite sync signal to frequency counter. To improve the driving ability, it is possible to connect a resister (minimum: $2 \ k\Omega$ ) between this pin and GND. However, when the resister is added, the output DC voltage is down. | 8<br>0 000 Ω<br>0 000 Ω<br>(14)                         | DC<br>or<br>H/C SYNC<br>———————————————————————————————————— |

| 10         | VD3-IN                  | Inputs vertical sync signal.  Accepts input of both positive and negative polarity.                                                                                                                                                                                                   | 1 kΩ                                                    | or Th: 0.7 V                                                 |

| 11         | HD3-IN                  | Inputs horizontal sync signal. Accepts input of both positive and negative polarity.                                                                                                                                                                                                  | (1) 1 KG (W) 09 (S) | or Th: 0.7 V                                                 |

| Pin<br>No. | Pin Name    | Function                                                                                                                                                | Interface Circuit | Input Signal/Output Signal |

|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|

| 12         | CP-OUT      | Clamp pulse (CP) output pin. Outputs CP generated by sync circuit.                                                                                      | 25 KΩ S (4)       | 5.0 V<br>0 V               |

| 13         | HD1-OUT     | HD output pin. Open collector output. HD1/HD2 input signal is output from this pin without synchronization. Polarity is switched by BUS write function. | 3 200 Ω<br>(14)   | or                         |

| 14         | Digital GND | GND pin for logic blocks.                                                                                                                               | _                 | _                          |

| Pin<br>No. | Pin Name | Function                                                                                                                                                | Interface Circuit                                     | Input Signal/Output Signal |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| 15         | HD2-OUT  | HD output pin. Open collector output. HD1/HD2 input signal is output from this pin without synchronization. Polarity is switched by BUS write function. | 8<br>200 Ω<br>W 14                                    | or                         |

| 16         | SDA      | SDA pin for I <sup>2</sup> C bus.                                                                                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                            |

| Pin<br>No. | Pin Name   | Function                                                                                                                                                                | Interface Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Input Signal/Output Signal   |

|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 17         | SCL        | SCL pin for I <sup>2</sup> C bus.                                                                                                                                       | 20 kΩ SCL SCL 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |

| 18         | Address SW | Slave address switch pin.  When this pin is connected to V <sub>CC</sub> (GND), used for DC/DD <sub>H</sub> (D8/D9 <sub>H</sub> ); when left open, DA/DB <sub>H</sub> . | 100 kΩ<br>15 kΩ<br>100 kΩ | DC/DD 9 V DC/DD 7.5 V  DA/DB |

Note 1: The signal format for SYNC1-IN (pin 21) and SYNC2-IN (pin 19)

NTSC (525I/60 Hz), PAL/SECAM (625I/50 Hz), NTSC Double Scan (525I/120 Hz), PAL/SECAM Double Scan (625I/100 Hz), 525P/60 Hz, 750P/60 Hz, 1125I/60 Hz, 1125P/30 Hz

This IC doesn't have the sync-separation circuit for non-standard signals like weak strength signal, ghost signal and so on.

Note 1: The signal format for SYNC1-IN (pin 21) and SYNC2-IN (pin 19)

NTSC (525I/60 Hz), PAL/SECAM (625I/50 Hz), NTSC Double Scan (525I/120 Hz), PAL/SECAM Double Scan (625I/100 Hz), 525P/60 Hz, 750P/60 Hz, 1125I/60 Hz, 1125P/30 Hz

This IC doesn't have the sync-separation circuit for non-standard signals like weak strength signal, ghost signal and so on.

# **TOSHIBA**

| Pin<br>No. | Pin Name | Function                                                                                                                                                                                                                                                        | Interface Circuit | Input Signal/Output Signal          |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------|

| 23         | VD2-OUT  | VD output pin.  Open collector output.  VD1/VD2 input signal is output from this pin without synchronization.  Polarity is switched by BUS write function.  (Note) When HD PHASE will be changed, synchronized VD width will change. Use the start phase of VD. | 200 Ω (14)        | Start phase  or  Start phase        |

| 24         | DAC3     | DAC3 output pin.  Open collector output.  In Test mode, outputs test pulse for shipping.                                                                                                                                                                        | 8<br>500 Ω<br>14  | DC<br>or<br>test pulse for shipping |

## **Bus Control Map**

#### **Write Mode**

Slave Address: D8/DA/DCH

| Sub-Add | D7<br>MSB     | D6    | D5             | D4      | D3             | D2     | D1         | D0<br>LSB | Pre<br>MSB | eset<br>LSB |

|---------|---------------|-------|----------------|---------|----------------|--------|------------|-----------|------------|-------------|

| 00      | H-FREC        | UENCY | HD1/VD1-OUT SW |         | HD2/VD2-OUT SW |        | SEPA LEVEL |           | 1000       | 0000        |

| 01      | DA            | .C1   | DAC2           |         | DAC3           | TEST   | HD1-INV    | HD2-INV   | 1000       | 0000        |

| 02      | V-FREQUENCY ( |       |                | CLP-PHS | FREQ [         | DET SW | INPU       | TSW       | 1000       | 0000        |

| 03      |               |       | HD P           | HASE    |                |        | VD1-INV    | VD2-INV   | 1000       | 0000        |

#### **Read Mode**

Slave Address: D9/DB/DDH

|   | D7<br>MSB | D6 | D5              | D4  | D3       | D2  | D1 | D0<br>LSB |  |  |

|---|-----------|----|-----------------|-----|----------|-----|----|-----------|--|--|

| 0 | POR       |    |                 | VFF | REQUENCY | DET |    |           |  |  |

| 1 | HD-IN     |    | H FREQUENCY DET |     |          |     |    |           |  |  |

#### **Bus Control Functions**

## Write Mode (\*: Preset)

• H-FREQUENCY (Horizontal oscillation frequency)

Switches horizontal frequency.

(00): 15.75 kHz

(01): 31.5 kHz

\*(10): 33.75 kHz

(11): 45 kHz

• HD1/VD1-OUT SW (HD1/VD1 output switch)

Switches output from pin 13/22. When set to 00, 01, or 10, outputs HD/VD without synchronization. When set to 11, outputs HD/VD from the sync circuit. (Note) Synchronized VD width will change, when HD PHASE will be changed.

\*(00): HD1/VD1

(01): HD2/VD2

(10): HD3/VD3

(11): Synchronized HD/VD

• HD2/VD2-OUT SW (HD2/VD2 output switch)

Switches output from pin 15/23. When set to 00, 01, or 10, outputs HD/VD without synchronization. When set to 11, outputs HD/VD from the sync circuit.

\*(00): HD1/VD1

(01): HD2/VD2

(10): HD3/VD3

(11): Synchronized HD/VD

• SEPA LEVEL (Sync separation level switch)

Switches sync separation level of pin 19/21. Set values are the levels from sync tip. Sync separation level is changed according to the ratio of H-SYNC width during 1H period.

\*(00): 10IRE

(01): 15IRE

(10): 20IRE

(11): 25IRE (at 1125I/60)

• DAC1 (DAC1 control)

Controls 2-bit DAC (pin 9).

(00): 1 V

(01): 3 V

\*(10): 5 V

(11): 7 V

• DAC2 (DAC2 control)

Controls 2-bit DAC (pin 20).

\*(00): 1 V

(01): 3 V

(10): 5 V

(11): 7 V

• DAC3 (DAC3 control)

Controls open collector 1-bit DAC (pin 24).

\*(0): OPEN (HIGH)

(1): ON (LOW)

TEST (Test mode)

Switches DAC1, 2, and 3 outputs. Also used to test IC for shipping.

\*(0): DAC outputs are used as DAC.

(1): DAC1 outputs V. SYNC to the frequency counter.

DAC2 outputs H. SYNC or C. SYNC to the frequency counter.

DAC3 outputs IC test pulse for shipping.

• HD1-INV (HD1 output polarity switch)

Switches HD1 output (pin 13) polarity. When set to 0, positive HD input is output as negative HD. When set to 0, output from the sync circuit is output as negative HD.

\*(0): Normal (1): Inverse

• HD2-INV (HD2 output polarity switch)

Switches HD1 output (pin 15) polarity. When set to 0, positive HD input is output as negative HD. When set to 0, output from the sync circuit is output as negative HD.

\*(0): Normal (1): Inverse

• V-FREQUENCY (Vertical frequency switch (pull-in range))

Sets vertical frequency pull-in range, VD-STOP, or free-running frequency.

Free-running frequency is controlled by H-FREQUENCY.

|                 | Pull-in Range                                                                                                | Format/H (V) Frequency                                                  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| *( <u>000</u> ) | 48~1281 H                                                                                                    | 1125P/30 Hz (33.75 kHz)                                                 |  |  |

| (001)           | 48~849 H 750P/60 Hz (45 kHz)                                                                                 |                                                                         |  |  |

| (010)           | 010) FREE-RUN Free-running frequency is controlled by H-FREQUI (00): 262 H (01): 525 H (10): 562 H (11): 750 |                                                                         |  |  |

| (011)           | 48~637 H                                                                                                     | 1125I/60 Hz (33.75 kHz)                                                 |  |  |

| (100)           | 48~613 H                                                                                                     | 525P/60 Hz (31.5 kHz)                                                   |  |  |

| (101)           | 48~363 H                                                                                                     | PAL/SECAM/50 Hz (15.625 kHz)<br>PAL/SECAM double scan/100 Hz (31.5 kHz) |  |  |

| (110)           | 48~307 H                                                                                                     | NTSC/60 Hz (15.734 kHz)<br>NTSC double scan /120 Hz (31.5 kHz)          |  |  |

| (111)           | VP STOP                                                                                                      | VD output is HIGH                                                       |  |  |

• CLP PHS (Clamp pulse phase switch)

Switches clamp pulse phase.

If no signal input, 0.9 µs pulse is output from the H-C/D circuit.

\*(0): 1 μs (3.4%) delay following HD stop phase, 0.8 μs (2.7%) pulse

(1):  $0.5 \mu s$  (1.7%) delay following HD stop phase,  $0.8 \mu s$  (2.7%) pulse

• FREQ DET SW (Horizontal/vertical frequency counter switch)

Switches input signal used for horizontal/vertical frequency counter. This switch is controlled independently from INPUT SW. The detection result is output as read BUS data.

\*(00): SYNC1 input (01): SYNC2 input (10)/(11): HD3/VD3 inputs

• INPUT SW (Input signal switch for synchronization)

Switches input signal used for synchronization.

\*(00): SYNC1 input (01): SYNC2 input (10)/(11): HD3/VD3 inputs

• HD PHASE (HD phase adjustment)

Adjusts phase of HD output from the sync circuit. The phase of the adjustment center value is the same as that of input H-SYNC or input HD. (Note) Synchronized VD width will change, when HD PHASE will be changed.

(000000): -5% (H periodically)

\*(100000): 0% (111111): 5%

• VD1-INV (VD1 output polarity switch)

Switches VD1 output (pin 22) polarity. When set to 0, negative VD input is output as negative VD. When set to 0, output from the sync circuit is output as negative VD.

\*(0): Normal (1): Inverse

• VD2-INV (VD2 output polarity switch)

Switches VD2 output (pin 23) polarity. When set to 0, negative VD input is output as negative VD. When set to 0, output from the sync circuit is output as negative VD.

\*(0): Normal (1): Inverse

#### **Read Mode**

- POR (Power on reset)

- (0): Status read (at second data read and subsequent)

- (1): Power on (at first data read)

- HD-IN (Input signal self-check result)

Detects HD or H-SYNC input signal selected by INPUT SW.

(0): No signal input (1): Signal input

V FREQ DET (Vertical frequency of SYNC or VD input selected by FREQ DET SW)

(0000000)~(0001100): No-VD (0001101): Vicinity of 162 Hz (1111110): Vicinity of 17 Hz

How to calculate vertical frequency (X):

Convert V-FREQ DET read data into decimal and define the resulting value as Y.

Where H-FREQUENCY is 15.75 kHz/31.5 kHz,  $Z = 476.2 \mu s$

Where H-FREQUENCY is 33.75 kHz/45 kHz,  $Z = 474.1 \mu s$

Vertical frequency (X) =  $1 \div (Y \times Z)$  [Hz]

Error of Y is +1, -0. If vertical frequency is 162 Hz or more, the frequency cannot be accurately measured. Time constant used to separate V.SYNC from integrated C.SYNC is 9  $\mu$ s (error:  $\pm 1 \mu$ s).

H FREQ DET (Horizontal frequency of SYNC or HD input selected by FREQ DET SW)

(0000000): No signal input (1111110): 53 kHz or more

How to calculate horizontal frequency (X):

X, Y, and Z are defined same as for V FREQ.

Horizontal frequency (X) =  $Y \div (5 \times Z)$  [kHz]

Error of Y is +1, -0. If horizontal frequency is 53 kHz or more, the frequency cannot be accurately measured. When V-SYNC or VD is not input, horizontal frequency cannot be measured, resulting in data = (0000000).

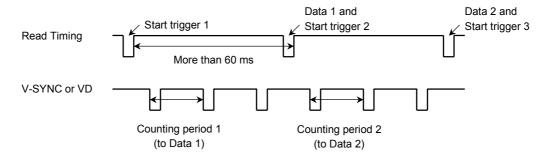

Note 1: The start trigger for frequency counting is the internal reset-pulse made from ACK of 2nd byte in BUS read mode. The counting period is between the first V-sync (VD) and the second V-sync (VD) after the trigger.

The counted data will have +1 or -0 error according to the read timing.

To assume stable data reading;

- 1. Set BUS reading interval more than 60 ms.

- 2. Don't use the first data because it is unsettled.

are recommended.

Note 2:Ignore data (1111111). This data may be obtained in case the trigger pulse and the V-sync (VD) are simultaneous.

Decision algorithm (detection range, detection times and so on) should be determined under consideration of Note 1, Note 2 and the other factors such as signal strength, existence of ghost signal, H-AFC stability, I<sup>2</sup>C BUS data transmission and so on via prototype TV set evaluation.

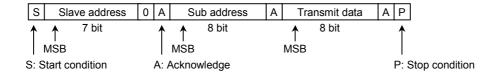

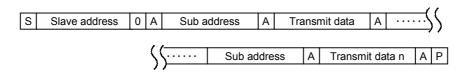

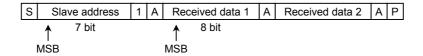

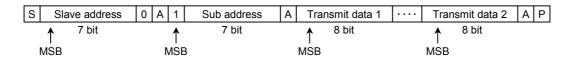

# Data Transfer Format via I<sup>2</sup>C BUS

## Slave Address: D8/DA/DCH

| A6 | A5 | A4 | A3 | A2 | A1  | A0  | W/R |

|----|----|----|----|----|-----|-----|-----|

| 1  | 1  | 0  | 1  | 1  | 0/1 | 0/1 | 0/1 |

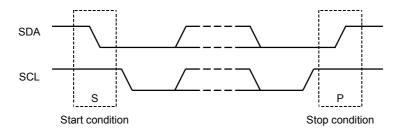

## **Start and Stop Condition**

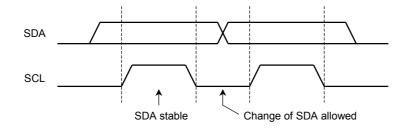

#### **Bit Transfer**

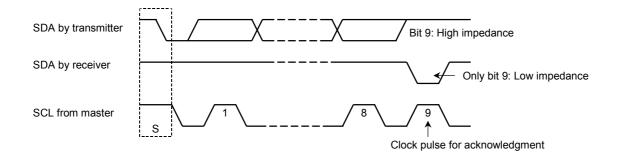

# Acknowledge

#### **Data Transmit Format 1**

#### **Data Transmit Format 2**

#### **Data Receive Format**

At the moment of the first acknowledge, the master transmitter becomes a master receiver and the slave transmitter. This acknowledge is still generated by this slave.

The Stop condition is generated by the master.

(\* important) The data read from THIS IC should always be completed in whole two words, not one word, otherwise the IICBUS may cause error.

#### **Optional Data Transmit Format: Automatic Increment Mode**

In this transmission method, data is set on automatically incremented sub-address from the specified sub-address.

Purchase of TOSHIBA  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

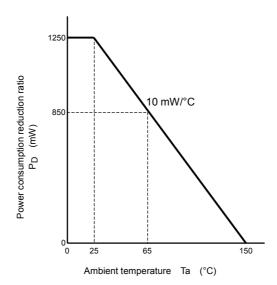

# Maximum Ratings (Ta = 25°C)

| Characteristics                  | Symbol              | Rating  | Unit             |

|----------------------------------|---------------------|---------|------------------|

| Supply voltage                   | V <sub>CCmax</sub>  | 12      | V                |

| Input pin signal voltage         | e <sub>inmax</sub>  | 9       | V <sub>p-p</sub> |

| Power dissipation                | P <sub>D</sub> (*1) | 1250    | mW               |

| Power dissipation reduction rate | 1/Qja               | -10     | mW/°C            |

| Operating temperature            | T <sub>opr</sub>    | -20~65  | °C               |

| Storage temperature              | T <sub>stg</sub>    | -55~150 | °C               |

Note: Refer to the figure below.

Figure P<sub>D</sub> - Ta Curve

# **Operating Condition**

| Characte                                | eristics             |                 | Description                 | Min        | Тур. | Max   | Unit             |

|-----------------------------------------|----------------------|-----------------|-----------------------------|------------|------|-------|------------------|

| Power supply voltage                    | e (V <sub>CC</sub> ) | Pin 8           |                             | 8.5        | 9.0  | 9.5   | V                |

| HD1, HD2, HD3 Inpu                      | ut level             | Pin 3, 1, 11    |                             | 2.0        | 5.0  | 9.0   | \/               |

| VD1, VD2, VD3 Inpu                      | it level             | Pin 4, 2, 10    |                             | 2.0        | 5.0  | 9.0   | V <sub>p-p</sub> |

|                                         | Synchronization      | Pin 11          |                             | 0.02       | _    | 0.20  | Н                |

| HD3 input width                         | Frequency detection  | Pin 11          |                             | 0.45<br>μs | _    | 0.25H | _                |

|                                         | Synchronization      | Pin 10          |                             | 1 μs       | _    | 47H   | _                |

| VD3 input width                         | Frequency detection  | Pin 10          |                             | 1          | _    | 400   | μS               |

| SYNC1, SYNC2 Inp                        | ut level             | Pin 21, 19, whi | ite 100% with negative sync | 0.9        | 1.0  | 1.1   | V <sub>p-p</sub> |

| HD1, HD2, VD1, VD2-OUT<br>Input current |                      | Pin 13, 15, 22, | 23                          | _          | 0.9  | 1.5   | mA               |

| DAC3 Input current                      |                      | Pin 24          |                             | _          | 0.5  | 1.0   |                  |

| Address switching voltage               |                      | Din 10          | D8/D9 <sub>H</sub>          | 0          | 0    | 1.0   | \/               |

|                                         |                      | Pin 18          | DC/DD <sub>H</sub>          | 8.0        | 9.0  | 9.0   | V                |

18

# Electrical Characteristics ( $V_{CC} = 9 V$ , Ta = 25°C, unless otherwise specified)

# **Current Dissipation**

| Pin Name        | Symbol | Test<br>Circuit | Min | Тур. | Max | Unit |

|-----------------|--------|-----------------|-----|------|-----|------|

| V <sub>CC</sub> | Icc    | _               | 32  | 38   | 44  | mA   |

#### **AC Characteristics**

## **Horizontal Block**

| Characteristics                                                                                         | Symbol                           | Test<br>Circuit | Test Condition | Min   | Тур.  | Max   | Unit             |  |

|---------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|----------------|-------|-------|-------|------------------|--|

| Sync1/2 input horizontal sync phase                                                                     | S <sub>1PH</sub>                 | _               | (Note HA01)    | 0.6   | 0.7   | 0.8   | 6                |  |

| Sync 1/2 input nonzontal sync phase                                                                     | S <sub>2PH</sub>                 | _               | (Note HA01)    | 0.6   | 0.7   | 0.8   | μS               |  |

| HD3 input horizontal sync phase                                                                         | HD <sub>3PH</sub>                | _               | (Note HA02)    | 0.6   | 0.7   | 0.8   | μS               |  |

| Polarity distinction active range                                                                       | HD- <sub>DUTY1</sub>             | _               | (Note HA03)    | 61    | 66    | 71    | %                |  |

| Folanty distinction active range                                                                        | HD- <sub>DUTY2</sub>             | _               | (Note HA03)    | 48    | 53    | 58    | 70               |  |

|                                                                                                         | V <sub>thS10</sub>               | _               |                | 0.040 | 0.070 | 0.100 |                  |  |

|                                                                                                         | V <sub>thS11</sub>               | _               |                | 0.060 | 0.106 | 0.152 |                  |  |

|                                                                                                         | V <sub>thS12</sub>               | _               |                | 0.081 | 0.142 | 0.203 |                  |  |

| Sync1 input threshold amplitude                                                                         | V <sub>thS13</sub> — (Note HA04) |                 | 0.102          | 0.178 | 0.255 | V     |                  |  |

| Sync2 input threshold amplitude                                                                         | V <sub>thS20</sub>               | _               | (Note HA04)    | 0.040 | 0.070 | 0.100 | V <sub>p-p</sub> |  |

|                                                                                                         | V <sub>thS21</sub>               | _               |                | 0.060 | 0.106 | 0.152 |                  |  |

|                                                                                                         | V <sub>thS22</sub>               | _               |                | 0.081 | 0.142 | 0.203 |                  |  |

|                                                                                                         | V <sub>thS23</sub>               | _               |                | 0.102 | 0.178 | 0.255 |                  |  |

| HD3 input threshold amplitude (Synchronization block)                                                   | V <sub>thHD3</sub>               |                 | (Note HA05)    | 0.65  | 0.75  | 0.85  | V <sub>p-p</sub> |  |

| HD1 input threshold voltage<br>HD2 input threshold voltage<br>HD3 input threshold voltage<br>(SW block) | V <sub>thHD1</sub>               | _               |                | 0.65  | 0.75  | 0.85  |                  |  |

|                                                                                                         | V <sub>thHD2</sub>               | _               | (Note HA06)    | 0.65  | 0.75  | 0.85  | V <sub>p-p</sub> |  |

|                                                                                                         | V <sub>thHD3</sub>               | _               |                | 0.65  | 0.75  | 0.85  |                  |  |

|                                                                                                         | ΔΗΡ0-                            |                 |                | 2.86  | 3.18  | 3.49  |                  |  |

|                                                                                                         | ΔΗΡ0+                            | _               |                | 2.86  | 3.18  | 3.49  |                  |  |

|                                                                                                         | ΔΗΡ1–                            | _               |                | 1.43  | 1.59  | 1.75  |                  |  |

| HD output phase adjustment variable                                                                     | ΔHP1+                            | _               | (Note HA07)    | 1.43  | 1.59  | 1.75  | 0                |  |

| range                                                                                                   | ΔHP2-                            | _               | (Note HA07)    | 1.33  | 1.48  | 1.63  | μS               |  |

|                                                                                                         | ΔHP2+                            | _               |                | 1.33  | 1.48  | 1.63  |                  |  |

|                                                                                                         | ΔΗΡ3-                            | _               |                | 1.00  | 1.11  | 1.22  |                  |  |

|                                                                                                         | ΔHP3+                            | _               |                | 1.00  | 1.11  | 1.22  |                  |  |

|                                                                                                         | CP <sub>S0</sub>                 | _               |                | 0.85  | 1.00  | 1.15  | 0                |  |

|                                                                                                         | CP <sub>W0</sub>                 | _               |                | 0.65  | 0.80  | 0.95  | μS               |  |

|                                                                                                         | CP <sub>V0</sub>                 | _               |                | 4.7   | 5.0   | 5.3   | V                |  |

|                                                                                                         | CP <sub>S1</sub>                 | _               |                | 0.35  | 0.50  | 0.65  | 0                |  |

| Clamp pulse phase/width/level                                                                           | CP <sub>W1</sub>                 | _               | (Note HA08)    | 0.65  | 0.80  | 0.95  | μS               |  |

|                                                                                                         | CP <sub>V1</sub>                 | _               |                | 4.7   | 5.0   | 5.3   | V                |  |

|                                                                                                         | CP <sub>S3</sub>                 | _               |                | 0     | _     | 1     | - μs             |  |

|                                                                                                         | CP <sub>W3</sub>                 | _               |                | 0.50  | 0.90  | 1.30  |                  |  |

|                                                                                                         | CP <sub>V3</sub>                 | _               |                | 4.7   | 5.0   | 5.3   | V                |  |

| Characteristics                       | Symbol            | Test<br>Circuit | Test Condition | Min | Тур. | Max | Unit |

|---------------------------------------|-------------------|-----------------|----------------|-----|------|-----|------|

| Delayed HD pulse width                | W <sub>d-HD</sub> | _               | (Note HA09)    | 1.0 | 1.2  | 1.4 | μS   |

|                                       | V13TH0            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V13TL0            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V13TH1            | _               |                | 4.5 | 5.0  | 5.5 |      |

| LID4 cutout valtage                   | V13TL1            | _               |                | _   | 0.1  | 0.5 |      |

| HD1 output voltage                    | V13TH2            | _               | _              | 4.5 | 5.0  | 5.5 | V    |

|                                       | V13TL2            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V13TH3            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V13TL3            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15TH0            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V15TL0            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15TH1            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V15TL1            | _               |                | _   | 0.1  | 0.5 | .,   |

| HD2 output voltage                    | V15TH2            | _               | _              | 4.5 | 5.0  | 5.5 | V    |

|                                       | V15TL2            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15TH3            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V15TL3            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V13IH0            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V13IL0            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V13IH1            | _               |                | 4.5 | 5.0  | 5.5 |      |

| HD1 output voltage (polarity inverse) | V13IL1            | _               |                | _   | 0.1  | 0.5 | V    |

|                                       | V13IH2            | _               | _              | 4.5 | 5.0  | 5.5 |      |

|                                       | V13IL2            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V13IH3            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V13IL3            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15IH0            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V15IL0            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15IH1            | _               |                | 4.5 | 5.0  | 5.5 |      |

| UD0                                   | V15IL1            | _               |                | _   | 0.1  | 0.5 | .,   |

| HD2 output voltage (polarity inverse) | V15IH2            | _               | _              | 4.5 | 5.0  | 5.5 | V    |

|                                       | V15IL2            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | V15IH3            | _               |                | 4.5 | 5.0  | 5.5 |      |

|                                       | V15IL3            | _               |                | _   | 0.1  | 0.5 |      |

|                                       | ID1               | _               |                | 310 | 385  | 460 |      |

| AFC phase detection surrent           | ID2               | _               | (Note LIDOA)   | 310 | 385  | 460 |      |

| AFC phase detection current           | ID3               | _               | (Note HB01)    | 520 | 650  | 780 | μΑ   |

|                                       | ID4               | _               |                | 520 | 650  | 780 |      |

| VCO oscillation start voltage         | V <sub>VCO</sub>  | _               | (Note HB02)    | 3.9 | 4.2  | 4.5 | V    |

|                                       | TH00              | _               |                | 1.4 | 1.8  | 2.2 |      |

| HD output pulse width                 | TH01              | _               | (Note LIDOO)   | 1.4 | 1.8  | 2.2 | -    |

| (free-run)                            | TH10              | _               | (Note HB03)    |     | 1.8  | 2.2 | μS   |

|                                       | TH11              | _               |                | 1.4 | 1.8  | 2.2 |      |

| Characteristics                            | Symbol             | Test<br>Circuit      | Test Condition | Min   | Тур.   | Max   | Unit  |

|--------------------------------------------|--------------------|----------------------|----------------|-------|--------|-------|-------|

|                                            | F00                |                      |                | 15.59 | 15.75  | 15.91 |       |

|                                            | F01                | _                    |                | 31.19 | 31.5   | 31.82 |       |

| Horizontal free-run frequency              | F10                | _                    | (Note HB04)    | 33.41 | 33.75  | 34.09 | kHz   |

|                                            | F11                | _                    |                | 44.55 | 45     | 45.45 |       |

|                                            | F50                | _                    |                | 15.47 | 15.625 | 15.78 |       |

| Horizontal oscillation control sensitivity | BH00               | _                    |                | 2.4   | 3.0    | 3.6   |       |

|                                            | BH01               | _                    | (Note HB05)    | 4.8   | 6.0    | 7.2   | kHz/V |

|                                            | BH10               | _                    | (Note HB05)    | 4.8   | 6.0    | 7.2   |       |

|                                            | BH10               | _                    |                | 7.1   | 8.9    | 10.7  |       |

|                                            | VDAC <sub>10</sub> | _                    |                | 0.5   | 1.0    | 1.5   |       |

| DAC1 output voltage                        | VDAC <sub>11</sub> | VDAC <sub>11</sub> — |                | 2.7   | 3.0    | 3.3   | V     |

| DACT output voltage                        | VDAC <sub>12</sub> | _                    | _              | 4.7   | 5.0    | 5.3   | v     |

|                                            | VDAC <sub>13</sub> | _                    |                | 6.5   | 7.0    | 7.5   |       |

|                                            | VDAC <sub>20</sub> | _                    |                | 0.5   | 1.0    | 1.5   |       |

| DAC2 output voltage                        | VDAC <sub>21</sub> | _                    |                | 2.7   | 3.0    | 3.3   | V     |

| DAGE Gulpul Vollage                        | VDAC <sub>22</sub> | _                    | _              | 4.7   | 5.0    | 5.3   | V     |

|                                            | VDAC <sub>23</sub> | _                    |                | 6.5   | 7.0    | 7.5   |       |

| DAC3 output voltage                        | VDAC <sub>30</sub> | _                    |                | _     | 0.5    | 0.7   | - v   |

| DAGS output voitage                        | VDAC <sub>31</sub> | _                    | _              | 8.5   | 8.8    | _     |       |

# **Vertical Block**

| Characteristics                                            | Symbol             | Test<br>Circuit | Test Condition | Min    | Тур. | Max  | Unit             |

|------------------------------------------------------------|--------------------|-----------------|----------------|--------|------|------|------------------|

| VD1 input threshold voltage                                | V <sub>thVD1</sub> | _               |                | 0.65   | 0.75 | 0.85 |                  |

| VD2 input threshold voltage<br>VD3 input threshold voltage | V <sub>thVD2</sub> | _               | (Note VA01)    | 0.65   | 0.75 | 0.85 | V <sub>p-p</sub> |

| (SW block)                                                 | V <sub>thVD3</sub> | _               |                | 0.65   | 0.75 | 0.85 |                  |

| VD3 input threshold voltage (synchronization block)        | V <sub>thVD3</sub> | _               | (Note VA02)    | 0.65   | 0.75 | 0.85 | V <sub>p-p</sub> |

|                                                            | V22TH0             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V22TL0             | _               |                | _      | 0.1  | 0.5  |                  |

|                                                            | V22TH1             | _               |                | 4.5    | 5.0  | 5.5  |                  |

| ND4                                                        | V22TL1             | _               |                | _      | 0.1  | 0.5  | ,,               |

| VD1 output voltage                                         | V22TH2             | _               | _              | 4.5    | 5.0  | 5.5  | V                |

|                                                            | V22TL2             | _               |                | _      | 0.1  | 0.5  |                  |

|                                                            | V22TH3             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V22TL3             | _               |                | _      | 0.1  | 0.5  |                  |

|                                                            | V23TH0             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23TL0             | _               |                | _      | 0.1  | 0.5  |                  |

| VD2 output voltage                                         | V23TH1             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23TL1             | _               |                | _      | 0.1  | 0.5  | V                |

|                                                            | V23TH2             | <u> </u>        | _              | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23TL2             | _               |                | _      | 0.1  | 0.5  |                  |

|                                                            | V23TH3             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23TL3             | _               |                | _      | 0.1  | 0.5  |                  |

|                                                            | V22IH0             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V22IL0             | _               |                |        | 0.1  | 0.5  |                  |

|                                                            | V22IH1             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V22IL1             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

| VD1 output voltage (polarity inverse)                      | V22IH2             | <u> </u>        | _              | 4.5    | 5.0  | 5.5  | V                |

|                                                            | V22IL2             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

|                                                            | V22IH3             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V22IL3             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

|                                                            | V23IH0             | _               |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23IL0             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

|                                                            | V23IH1             | <u> </u>        |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23IL1             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

| VD2 output voltage (polarity inverse)                      | V23IH2             | <u> </u>        | _              | 4.5    | 5.0  | 5.5  | V                |

|                                                            | V23IL2             | <u> </u>        |                |        | 0.1  | 0.5  |                  |

|                                                            | V23IH3             |                 |                | 4.5    | 5.0  | 5.5  |                  |

|                                                            | V23IL3             |                 |                | —<br>— | 0.1  | 0.5  |                  |

|                                                            | VP <sub>W0</sub>   |                 |                | 251    | 286  | 321  |                  |

|                                                            | VP <sub>W1</sub>   |                 |                | 126    | 143  | 160  | -                |

| Vertical output pulse width                                | VP <sub>W1</sub>   |                 | (Note VA03)    |        | 133  | 150  | – μs<br>–        |

|                                                            |                    |                 |                |        | 100  |      |                  |

|                                                            | VP <sub>W3</sub>   | _               |                | 88     | 100  | 112  |                  |

# **TOSHIBA**

| Characteristics             | Symbol    | Test<br>Circuit | Test Condition | Min   | Тур.  | Max   | Unit |  |  |

|-----------------------------|-----------|-----------------|----------------|-------|-------|-------|------|--|--|

|                             | FV0       | _               |                | 26.02 | 26.35 | 26.67 |      |  |  |

| Vertical free-run frequency | FV1       | _               |                | 39.21 | 39.75 | 40.30 |      |  |  |

|                             | FV3       | _               |                | 52.20 | 52.98 | 53.77 |      |  |  |

|                             | FV4       | _               |                | 54.24 | 55.06 | 55.89 |      |  |  |

|                             | FV5       | _               | (Note VA04)    | 91.28 | 92.98 | 94.69 | Hz   |  |  |

|                             | FV6       | _               | (Note VAO+)    | 107.8 | 109.9 | 112.1 | 112  |  |  |

|                             | FV20      | _               |                | 57.0  | 60.0  | 63.0  |      |  |  |

|                             | FV21      |                 |                | 57.0  | 60.0  | 63.0  |      |  |  |

|                             | FV22      | _               |                | 57.0  | 60.0  | 63.0  |      |  |  |

|                             | FV23      | _               |                | 57.0  | 60.0  | 63.0  |      |  |  |

|                             | FVPL0     | _               |                | 311   | 321   | 332   |      |  |  |

| Vertical pull-in range      | FVPL1     | _               | (Note VA05)    | 624   | 643   | 663   | U→   |  |  |

| vertical pull-in range      | FVPL2     | _               | (Note VA05)    | 668   | 689   | 710   | Hz   |  |  |

|                             | FVPL3     | _               |                | 891   | 918   | 947   |      |  |  |

|                             | 15.75 kHz | _               |                | 9.6   | 11.8  | 14.0  |      |  |  |

| Sync input-VD output phase  | 31.50 kHz | _               |                | 5.7   | 6.8   | 7.9   | 0    |  |  |

| difference                  | 33.75 kHz | _               | _              | 5.3   | 6.4   | 7.5   | μS   |  |  |

|                             | 45.00 kHz | _               |                | 4.4   | 5.2   | 6.0   |      |  |  |

# **Test Conditions and Measuring Method**

| Note | Item                                |     | SW Mode |          |              | Test Conditions and Measuring Method (V $_{CC}$ = 9 V, Ta = 25 $\pm$ 3°C, unless otherwise specified) |

|------|-------------------------------------|-----|---------|----------|--------------|-------------------------------------------------------------------------------------------------------|

|      |                                     | S06 | S18     | S19      | S21          |                                                                                                       |

| HA01 | Sync1/2 input horizontal sync phase | С   | b       | а        | b            | (1) Set sub-address (02) 60.                                                                          |

|      |                                     |     |         | <b>↓</b> | $\downarrow$ | (2) SW19-a and SW21-b.                                                                                |

|      |                                     |     |         | b        | а            | (3) Input Signal a (horizontal 33.75 kHz ) to pin 21 (SYNC1-IN).                                      |

|      |                                     |     |         |          |              | (4) Set sub-address (02) 61.                                                                          |

|      |                                     |     |         |          |              | (5) Measure the phase difference S <sub>1PH</sub> between pin 21 and pin 6 (AFC filter) wave form.    |

|      |                                     |     |         |          |              | (6) SW19-b and SW21-a.                                                                                |

|      |                                     |     |         |          |              | (7) Input Signal a (33.75 kHz ) to pin 19 (SYNC2-IN).                                                 |

|      |                                     |     |         |          |              | (8) Set sub-address (02) 01.                                                                          |

|      |                                     |     |         |          |              | (9) Measure the phase difference S <sub>2PH</sub> between pin 19 and pin 6 (AFC filter) wave form.    |

|      |                                     |     |         |          |              |                                                                                                       |

|      |                                     |     |         |          |              | 29.63 μs                                                                                              |

|      |                                     |     |         |          |              | → ← 0.593 μs                                                                                          |

|      |                                     |     |         |          |              | Signal a 0.285 V                                                                                      |

|      |                                     |     |         |          |              |                                                                                                       |

|      |                                     |     |         |          |              | Pin 6 wave form   → S <sub>1PH</sub> ·S <sub>2PH</sub>                                                |

|      |                                     |     |         |          |              |                                                                                                       |

|      |                                     |     |         |          |              |                                                                                                       |

| Note | Item                              |     | SWI | Mode |     | Test Conditions and Measuring Method ( $V_{CC}$ = 9 V, $Ta$ = 25 $\pm$ 3°C, unless otherwise specified)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-----------------------------------|-----|-----|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                   | S06 | S18 | S19  | S21 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HA02 | HD3 input horizontal sync phase   | С   | b   |      | _   | <ul> <li>(1) Set sub-address (00) 40 and (02) 82.</li> <li>(2) Input signal b (horizontal 31.5 kHz ) to pin 11 (HD3-IN).</li> <li>(3) Measure the phase difference HD<sub>3PH</sub> between pin 11 and pin 6 (AFC filter) wave form.</li> </ul>                                                                                                                                                                                                                                                                                                                                                              |

| HA03 | Polarity distinction active range | С   | b   |      |     | <ul> <li>(1) Set sub-address (00) 70 and (02) 82.</li> <li>(2) Input signal b ((horizontal 31.5 kHz ) to pin 11 (HD3-IN).</li> <li>(3) Decreasing the duty of signal b to 0% (get negative period shorter), measure the duty of Signal b (HD-DUTY1) when the phase between pin 11 and pin 13 (HD1-OUT) change.</li> <li>(4) Increasing the duty of Signal b to 100% (get negative period longer), measure the duty of Signal b (HD-DUTY2) when the phase between pin 11 and pin 13 (HD1OUT) change.</li> <li>Signal b</li> <li>* 31.75 μs</li> <li>31.75 μs</li> <li>4 duty = A/(A + B) × 100 (%)</li> </ul> |

| Note | ltem                                                  |     | SWI | Mode         |              | Test Conditions and Measuring Method (V $_{CC}$ = 9 V, Ta = 25 $\pm$ 3°C, unless otherwise specified)                                                        |

|------|-------------------------------------------------------|-----|-----|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                       | S06 | S18 | S19          | S21          |                                                                                                                                                              |

| HA04 | Sync1 input threshold amplitude                       | С   | b   | а            | b            | (1) Set sub-address (00) 0B and (02) 60.                                                                                                                     |

|      | Sync2 input threshold amplitude                       |     |     | $\downarrow$ | $\downarrow$ | (2) Input Signal a (33.75 kHz) to pin 21 (SYNC1-IN)                                                                                                          |

|      |                                                       |     |     | b            | а            | (3) Measure the sync. tip DC voltage of signal a on pin 21 (SYNC1-IN). (V <sub>sync11</sub> )                                                                |

|      |                                                       |     |     |              |              | (4) Supply external voltage via 100 k $\Omega$ to pin 21 and increase the voltage.                                                                           |

|      |                                                       |     |     |              |              | (5) Measure the sync. tip DC voltage ( $V_{sync12}$ ) when HD-OUT desynchronizes with signal a calculate $V_{thS10}$ . $V_{thS10} = V_{sync12} - V_{sync11}$ |

|      |                                                       |     |     |              |              | (6) Set sub-address (00) B1, B2 and B3 and calculate V <sub>thS11</sub> , V <sub>thS12</sub> and V <sub>thS13</sub> as well.                                 |

|      |                                                       |     |     |              |              | (7) Calculate V <sub>thS20</sub> , V <sub>thS21</sub> , V <sub>thS22</sub> and V <sub>thS23</sub> against pin 19 (SYNC2-IN) in the same way as 4 to 6.       |

|      |                                                       |     |     |              |              | 29.63 μs  ———————————————————————————————————                                                                                                                |

| HA05 | HD3 input threshold amplitude (synchronization block) | С   | b   | _            | _            | (1) Set sub-address (00) 70 and (02) 62.                                                                                                                     |

|      | (cyricinic in Education                               |     |     |              |              | (2) Input Signal b (31.5 kHz) to pin 11 (HD3-IN).                                                                                                            |

|      |                                                       |     |     |              |              | (3) Increasing the voltage of Signal b from 0 V, measure the voltage of Signal b V <sub>thHD3</sub> when HD1-OUT lock.                                       |

|      |                                                       |     |     |              |              | 31.75 μs                                                                                                                                                     |

| Note | Item                                                                                                    |     | SW I | Mode |     | Test Conditions and Measuring Method ( $V_{CC} = 9 \text{ V}$ , $Ta = 25 \pm 3^{\circ}\text{C}$ , unless otherwise specified)                                                                                                                                                                                                                                                                                        |  |  |  |

|------|---------------------------------------------------------------------------------------------------------|-----|------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      |                                                                                                         | S06 | S18  | S19  | S21 |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| HA06 | HD1 input threshold voltage<br>HD2 input threshold voltage<br>HD3 input threshold voltage<br>(SW block) | С   | b    | ı    |     | <ul> <li>(1) Set sub-address (00) 40.</li> <li>(2) Input Signal b (31.5 kHz) to pin 3 (HD1-IN).</li> <li>(3) Increasing the voltage of Signal b from 0 V, measure the voltage of Signal b V<sub>thHD1</sub> when HD1-OUT lock.</li> <li>(4) Measure the voltage of pin 1 V<sub>thHD2</sub>. Measure the voltage of pin 11 V<sub>thHD3</sub> as well.</li> <li>31.75 μs</li> <li>2.35 μs</li> <li>Signal b</li> </ul> |  |  |  |

| Note | Item                                |     | SW Mode |     |     | Test Conditions and Measuring Method (V $_{CC}$ = 9 V, Ta = 25 $\pm$ 3°C, unless otherwise specified)                       |

|------|-------------------------------------|-----|---------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------|

|      |                                     | S06 | S18     | S19 | S21 |                                                                                                                             |

| HA07 | HD output phase adjustment variable | С   | b       | _   | _   | (1) Set sub-address (00) 30.                                                                                                |

|      | range                               |     |         |     |     | (2) Input Signal b (horizontal period T = 63.5 μs) to pin 11 (HD3-IN).                                                      |

|      |                                     |     |         |     |     | (3) Set sub-address (02) 02.                                                                                                |

|      |                                     |     |         |     |     | (4) Change form 00 to 7C sub-address (03), then measure the phase change quantity (ΔHP0–) of pin 13<br>(HD1-OUT) wave form. |

|      |                                     |     |         |     |     | (5) Change form 80 to FC sub-address (03), then measure the phase change quantity (ΔHP0+) of pin 13 (HD1-OUT) wave form.    |

|      |                                     |     |         |     |     | (6) When horizontal period of Signal b is T = 31.75 $\mu$ s measure $\Delta$ HP1– and $\Delta$ HP1+ as well.                |

|      |                                     |     |         |     |     | (7) When horizontal period of Signal b is T = 29.63 $\mu$ s measure $\Delta$ HP2– and $\Delta$ HP2+ as well.                |

|      |                                     |     |         |     |     | (8) When horizontal period of Signal b is T = 22.22 $\mu$ s measure $\Delta$ HP3– and $\Delta$ HP3+ as well.                |

|      |                                     |     |         |     |     | Signal b  Pin 15 wave form data (00)  Pin wave form data (7C) (80)  Pin wave form data (FC)                                 |

| Note | Item                          |     | SW Mode |     |     | Test Conditions and Measuring Method ( $V_{CC}$ = 9 V, Ta = 25 $\pm$ 3°C, unless otherwise specified)                                                           |

|------|-------------------------------|-----|---------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                               | S06 | S18     | S19 | S21 |                                                                                                                                                                 |

| HA08 | Clamp pulse phase/width/level | С   | b       | _   | _   | (1) Set sub-address (00) B0.                                                                                                                                    |

|      |                               |     |         |     |     | (2) Input Signal a (horizontal 33.75 kHz) to pin 11 (HD3-IN).                                                                                                   |

|      |                               |     |         |     |     | (3) Set sub-address (02) 02.                                                                                                                                    |

|      |                               |     |         |     |     | (4) Measure the clamp pulse phase (CP <sub>S0</sub> ), width (CP <sub>W0</sub> ), output level (CP <sub>V0</sub> ) of pin 12 (CLP-OUT) against Signal a.        |

|      |                               |     |         |     |     | (5) Set sub-address (02) 12.                                                                                                                                    |

|      |                               |     |         |     |     | (6) Measure the clamp pulse phase (CP <sub>S1</sub> ), width (CP <sub>W1</sub> ), output level (CP <sub>V1</sub> ) of pin 12 (SCP-OUT) against Signal a.        |